By Barak Perlman

When it comes to innovating using FPGAs, no one is a greater expert than Microsoft Azure. As early as 2010, well before anyone had ever heard of a SmartNIC (a term Microsoft Azure actually coined), Microsoft demonstrated the first proof of concept that used FPGAs at scale to accelerate web searches on its Bing search engine. The company’s Project Catapult produced the first pilot program to deploy FPGA-enabled servers in a data center in 2013, which showed dramatic improvement in latency, running decision-tree algorithms 40 times faster than CPUs alone while actually reducing the number of servers.

By 2015, Microsoft deployed FPGAs at scale into its Azure public cloud, and within a year, its AccelNet program had introduced FPGA-based SmartNICs as the default hardware for implementing virtual network functions in Azure, deploying FPGAs in over one million hosts.

So when Azure released its recent Accelerated Networking white paper making a compelling case that FPGA-based SmartNICs are the optimal choice for cloud environments, the marketplace took notice.

Let’s examine some of the most striking points from the paper:

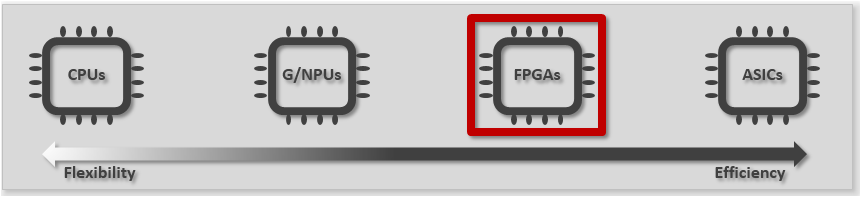

First, Azure compared four hardware options as solutions to the expanding networking challenges of the cloud:

- While ASIC-based NICs offered the highest performance potential, they lacked programmability, limiting their adaptability over time. The paper also states that adding a small number of CPU cores to ASICs does not provide the required programmability, as those CPU cores quickly become the bottleneck.

- Azure strongly recommended against using multicore system-on-chip (SoC) NICs, which offered the required programmability, but came at a great cost. Latency, power and price were limiting factors for multicore SmartNICs, and these considerations all rise precipitously when they scale beyond 40G, such that the solution is neither scalable nor futureproof.

- Adding additional host cores to manage pure software solutions offers the most flexibility in terms of programming. However, given that the core Azure business is providing Virtual Machines, sacrificing host cores to run the virtual switch, even with technologies such as DPDK, was too costly, both in terms of dollars and in terms of performance. Burning those cores essentially kills their public cloud business model.

- FPGAs, on the other hand, offered the performance and efficiency of customized hardware while enabling the programmability to adapt to new features, the ideal balance for optimizing their cloud.

Next, the Azure Accelerated Networking paper addressed many of the market’s typical concerns about FPGAs, explaining that in all cases, the benefit outweighed the (incorrect) negative perception. Perhaps the most important takeaway is that the perception that code is locked into a single FPGA vendor is debunked. Azure showed that it had very easily ported its code from Xilinx FPGAs in its initial foray into FPGAs in Project Catapult to Altera FPGAs in later development. This is critical, as multicore SmartNICs do not offer an easy means of avoiding vendor lock-in.

Azure also supported the accelerated networking ideas that FPGAs are by now data center-ready, reasonably priced given the yield, and reasonably sized given the benefits of increased programmability and configurability.

There was one area in which Azure suggested extreme caution when it comes to FPGAs. They urged that unless you are developing at a large enough scale (such as that of Azure) to justify the required investment in programming FPGAs, companies that seek to design their own FPGAs will find the task “daunting”. Rather, we think that it makes sense to partner with a company that has significant expertise in programming FPGAs, at least in the initial stages, until the right infrastructure, simulation capabilities, and programming tools have been established for further development.

This is where Ethernity Networks shines. We have 15 years of experience in developing FPGA-based networking solutions, offering hardware programmability at the pace of software development. Our patented ENET Flow Processor technology is uniquely designed to reduce die-size by up to 80%, enabling a rich networking feature set that provides the utmost performance at a reasonable cost. Most of all, Ethernity provides truly programmable network appliances that are both scalable and futureproof.

Take a valuable lesson from the industry experts: why take the chance by investing your valuable resources into developing your own FPGA SmartNICs, when Ethernity has a complete FPGA-based networking solution for you at a reasonable price today?