# **ENET Universal Edge Platform**

Ethernity's ENET Universal Edge Platform (UEP) is a modular network appliance targeted for network edge infrastructure solutions that offers up to 40Gbps of networking capacity and 10Gbps of IPSec VPN performance with virtually unlimited flexibility in protocol and port configurations, as well as a dual-core ARM processor for running the control stack.

The main board of the ENET UEP comes with two SFP+ interfaces that can be equipped with 10GbE or XGS-PON transceivers, and an FPGA equipped with Ethernity's ENET Flow Processor, implementing complete Carrier Ethernet switch, hierarchical QoS, router, IPSec, and optional XGS-PON MAC.

The ENET UEP offers optimum modularity through its interchangeable mezzanine card, which enables the appliance to be designed to support G.fast, enterprise Power over Ethernet (PoE) solutions, or additional connectivity via 1/10GbE interfaces. The default ENET UEP offers 8 x 1Gb RJ45 ports in the mezzanine card.

## **Product Highlights**

- Modular appliance

- 2 x 10GbE, or alternatively

1 x XGS-PON and 1 x 10GbE

- 8 x 1GbE, or optionally G.fast, PoE, and other port designs per customer request

- Low space, low power ideal for network edge infrastructure

- FPGA-based programmable flow processor to handle fully-compliant Carrier Ethernet switch, router, and hierarchical QoS

- IEEE 1588 and SyncE

- MPLS and PWE

- IPSec tunneling and other overlay methods: NVGRE, VxLAN, L2TP PPPoE

- Dual-core ARM processor to handle control plane functions

- PCle extender

- Connect any standard server running NFV environment to offload networking and security functions

With its embedded ARM processing cores that handle the control plane, the ENET UEP is a standalone high-end Network Interface Device (NID) that offers powerful router and IPSec functionality. The mezzanine card can also support IoT aggregation elements, for example, a radio modem for the IoT sensor network.

## **ENET UEP Applications**

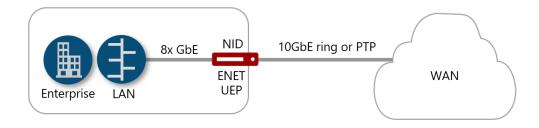

## **High-End NID**

Thanks to its two ARM processing cores, the ENET UEP is able to handle all control functions, while the onboard FPGA handles the data path. By combining this control with the 8 x 1Gb RJ45 ports in the standard mezzanine card, the ENET UEP is perfectly suited to serve as a high-end network interface device (NID) for demarcation of the WAN from the LAN networks. Moreover, the FPGA enables full routing functionality and IPSec security as add-ons to the NID, saving both space and cost at the network edge. The device can be arranged with 2 x 10GbE connectivity for LAG, ring, or cascading topologies, or with 1 x 10GbE and a second 10GbE port for 1:1 failover backup.

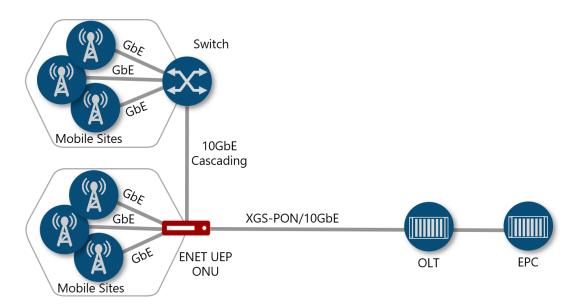

### **Mobile Backhaul with XGS-PON**

Thanks to its compact size and low power requirements, the ENET UEP is an ideal option for placement at cellular base stations, where it can provide cell site aggregation and XGS-PON connectivity with the optical line termination (OLT).

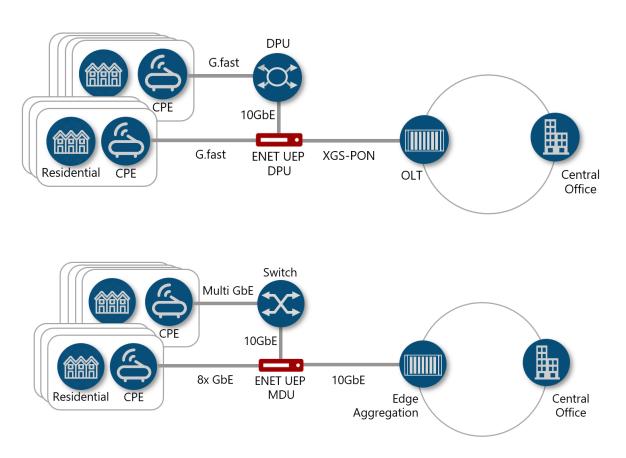

### DPU/MDU

The ENET UEP is uniquely positioned to be used as a distribution point unit (DPU) or multi-dwelling unit (MDU). It offers a 10G interface that can handle either Ethernet or XGS-PON, 8 x 1Gb Ethernet ports in its standard mezzanine card for distribution of fiber-to-the-building, and an additional 10G interface that can attach to any standard switch for even greater distribution capacity.

#### **PCIe Extender**

The ENET UEP comes with a PCIe connection to any standard server, enabling the network appliance to handle x86 functionality and NFV applications by offloading them to the built-in FPGA.

## **Specifications**

#### Interfaces

- 2 x SFP+ / 1 x SFP+ and 1 x XGS-PON

- 8 x RJ45

- PCIe Gen2 x4

- 1 PPS for precision time

#### General

- Flow-based processor with L2/3/4 flow classification, hierarchical ACL

- Search engine up to 256K entries

- · Switch, router, MPLS and load balancing functions

- Five-level packet header & payload manipulation and marking:

- MPLS

- PBB

- QinQ (PB)

- Different editing on duplicated packets/multicast

- Supported encapsulations:

- L2TP, PPPoE

- GRE, NVGRE, VxLAN

- IPinIP

- LAG (L2, L3, L4 distribution)

- ERPS, ELPS

- Wire speed NAT/NAPT

- IP fragmentation

#### Classification and Filtering

- Packet classification based on first 196 bytes in packet (can be extended)

- Configurable per flow functional actions:

- Filtering

- Trapping

- Mirroring

- Packet editing

- QoS remarking

- Hierarchical ACL, and mask configuration per field

- Rate dependent filters (e.g., limit rate of ingress IGMPv3 packets)

- Configurable control of MAC address learning per port/VLAN

#### **Timing**

For mobile deployments, the UEP offers SyncE and IEEE 1588v2 with ordinary, transparent, and boundary clock capabilities.

#### **Switching**

- L2 PB switching compliant with IEEE 802.1ad

- L2 unicast up to 256K MAC table

- L2 multicast up to 2K active multicast groups

- Switching based on inner MAC and combination of network tags and/or outer MAC and combination of network tags

- TR101, TR-156

#### **Traffic Management**

- Support of jumbo frames up to 9KB

- Hierarchical MEF10 metering:

- On port level

- On service level

- On flow level

- Any combination can be mapped to a specific meter

- Hierarchical, three-level scheduler per MEF10

- 256 virtual port each with 8 priority queues

- 2K queues

- Shaper per queue and each hierarchy:

- Packet level

- Byte level

- Configurable MTU per priority queues or per cluster

Per let Falitie a.

#### Packet Editing

- First 196 bytes editing, including QoS remarking, byte counts, sequence ID and DSCP, FCS calculation

- Header modification up to 48 bytes (push/pop/modify) for VLAN

- L2 and L3 loopbacks, including swap of MAC SA and DA, swap of IP

#### **IPSec**

- IPSec tunneling for both encryption and authentication

- Supported crypto algorithms

- AES 128/256

- SHA1/SHA2

- SHA-224

- SHA-256

- SHA-384

- SHA-512

### OAM

- Hardware support for CFM compliant with 802.1ag

- Support for four ME levels in compliance with TR-101 and TR-156

- Integrated packet generator and analyzer to support OAM packet generation and analysis per Y.1731, including per flow BERT

- Hardware processing for L2, L3 loopbacks (swap L2 SA/DA, swap L3 SA/DA)

- Hardware fast protecting switching within microseconds

#### Software

- ENET driver with ENET CLI with Application Guide

- ENET NPS full switch/router network protocol suite CPU

- ARM dual-core Cortex 9

#### **Integrated Optional XGS-PON MAC**

- US/DC MAC

- XGS-OLT ITU-G.9807.1 support for all mandatory requirements

**ENET UEP Ordering Options**

| Product<br>Name                       | Part Number | Product Description                                                                                                                                      |

|---------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENET<br>Universal<br>Edge<br>Platform | ENS1020Z    | Standalone network appliance with 2 x 10GbE ports (1:1), FPGA, ENET Flow Processor, dual-core ARM Processor, standard 8 x 1GbE mezzanine card            |

|                                       | ENS1030Z    | Standalone network appliance with 2 x 10GbE ports (1+1), FPGA, ENET Flow Processor, dual-core ARM Processor, standard 8 x 1GbE mezzanine card            |

|                                       | ENS1020ZX   | Standalone network appliance with 1 x XGS-PON port, 1 x 10GbE port, FPGA, ENET Flow Processor, dual-core ARM Processor, standard 8 x 1GbE mezzanine card |

The following ordering options comprise the complete UEP configuration on top of the base L2 switch and H-QoS that are included by default. When ordering, please specify the add-on features by appending a dash and the relevant code(s) to the product number:

I – PCI NIC; R – Router; T – Precision Time Protocol; S – Security (IPSec); M – MPLS support; P – SLA Prob (OAM); O – Overlay (VxLAN, NVGRE); 99 – DPU (G.fast interface)