The Market Need

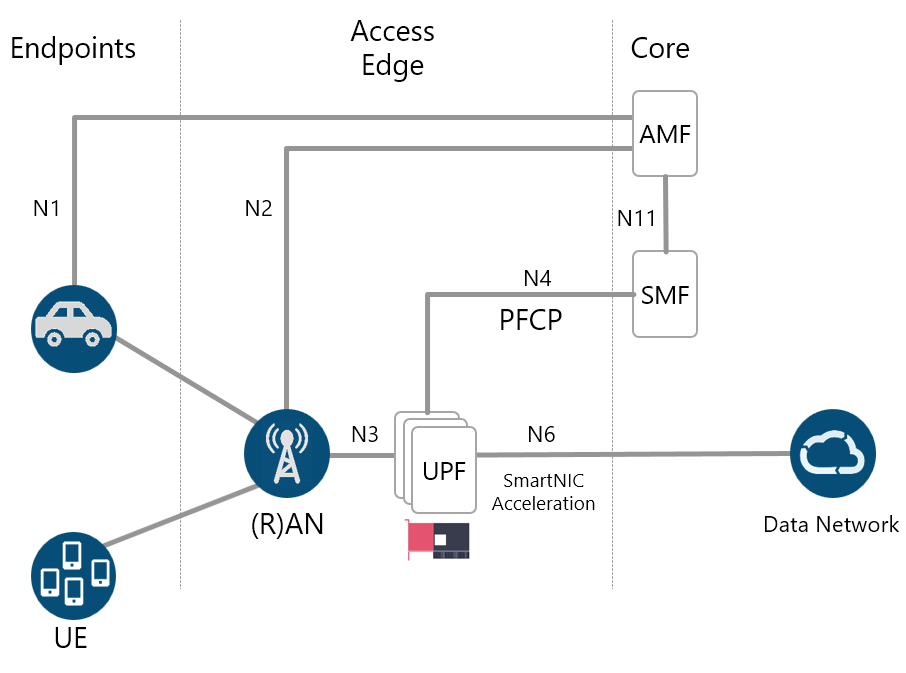

The 3GPP 5G specifications have been evolving in stages into the new CUPS (control and user plane separation) architecture, which is fundamental for 5G, and one of its primary functions is the User Plane Function (UPF). Today’s leading operators are using a disaggregation approach to their networks, and compute resources are being moved to the edge of the network closer to end-user locations, requiring a small physical footprint and low power. When this is combined with the requirements of high bandwidth, low latency, dense connectivity, and multitenancy to achieve 5G Quality of Experience, operators are hard-pressed to find a workable solution.

Our Offering

Ethernity Networks’ 5G UPF Forwarding Offload solution assures carrier-grade UPF performance at an extremely competitive price. The solution fits the disaggregation approach used by today’s leading operators by enabling the UPF to be placed at the network edge closer to end user locations, thereby achieving better performance, reducing networking overhead, improving latency, and lowering costs.

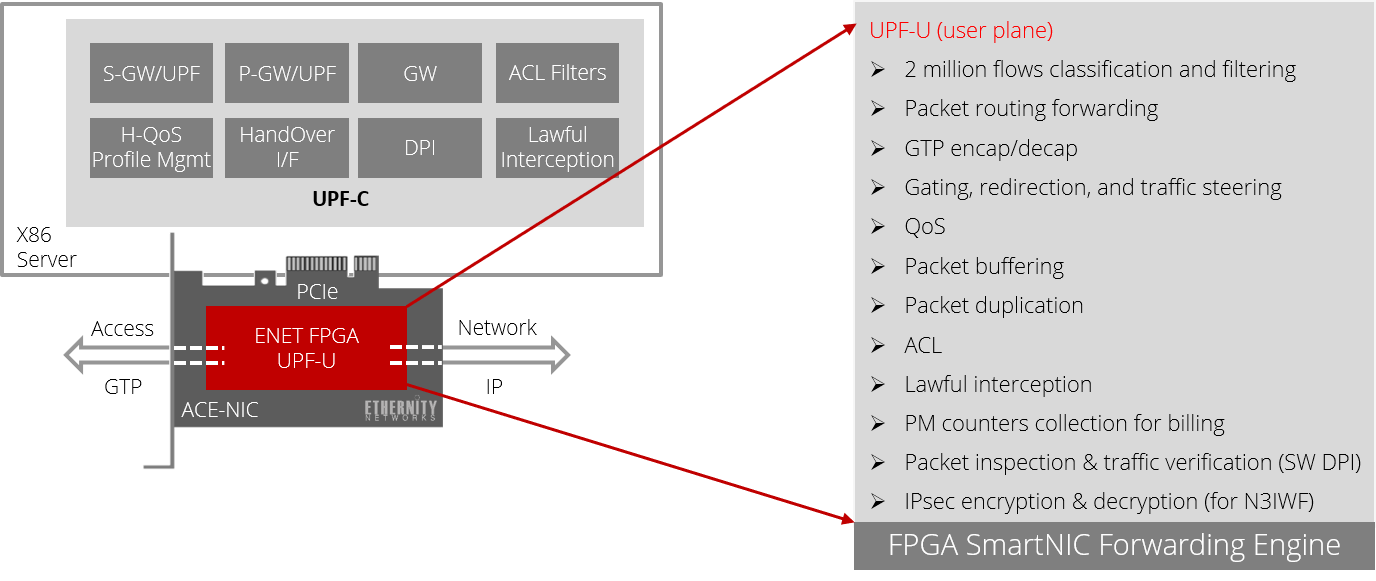

Ethernity’s FPGA-based ACE-NIC SmartNIC easily integrates with third-party UPF software networking elements from any vendor to fully offload the user plane traffic, releasing server CPU cores, enhancing scalability, and assuring deterministic performance. It enables an easily programmable future-ready data path that can quickly adapt to a service provider’s unique requirements and evolve with the ever-changing architectural requirements of the mobile market.

The ENET data path also supports network slicing with extensive multi-tenant control and with service partitioning and isolation features.

The solution is implemented using Ethernity’s ACE-NIC100 FPGA SmartNICs for accelerating 5G UPF as a VNF (virtual network functions). The ACE-NICs accelerate the network function virtualization infrastructure (NFVI) via standard DPDK APIs for fast integration. The solution is also available for implementation via Ethernity’s ENET L3 Flow Processor.

- Programmable (FPGA) data plane

- ASIC-like deterministic and low latency performance

- Scalable – multiple ACE-NICs FPGA SmartNICs for any capacity

- Very low power (sub-50W per ACE-NIC)

- Solves the problem of load balancing between different UPFs

- Better competitiveness by releasing valuable CPU cores for more user applications

- Enables flexible flow management, providing all aspects of fault, configuration, accounting, performance, and security information to the control stack

- Fast integration using standard DPDK APIs

- Fits any COTS server

UPF-U features offloaded by SmartNIC

- Packet routing forwarding

- GTP termination (if needed)

- Gating, redirection & traffic steering

- QoS

- Packet buffering

- Packet duplication

- ACL

- Lawful interception

- PM counters collection for billing

- IPsec encryption & decryption (for N3IWF)

Acceleration UPF in 5G

SmartNIC Accelerates UPF Features