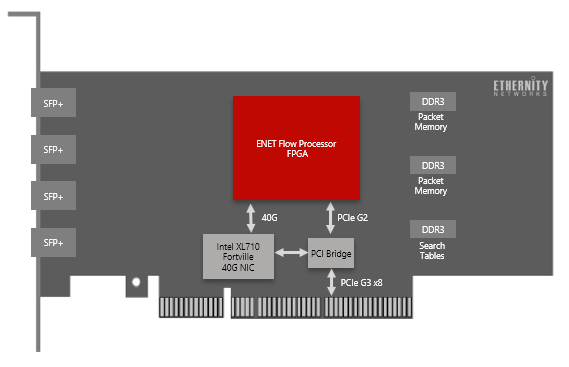

Ethernity’s ACE-NIC40 FPGA SmartNIC is a 40G programmable network adapter for NFV acceleration. With 4x10G ports, the ACE-NIC40 accelerates performance and dramatically reduces end-to-end latency associated with NFV platforms.

The Markets and Challenges

With the transition to SDN/NFV and programable networks, service providers are deploying more compute resources for networking and security, especially at the network edge. However, CPUs are less optimal for data handling, so it has become accepted that FPGA-based SmartNICs are a more efficient means of implementing networking and security.

Our Offering

Ethernity’s ACE-NIC40 is a 4 x 10G FPGA-based SmartNIC, ideal for operating on top of COTS servers. It significantly accelerates network function performance, dramatically reducing end-to-end latency associated with NFV platforms.

The ACE-NIC40 incorporates Ethernity’s ENET Flow Processor, which utilizes a patented unique flow-based processing engine to process data units of variable size. Our firmware has been integrated into the onboard FPGA to integrate the functionality of various network components, including NIC and SR-IOV support, as well as network processing, such as classification, virtual router and switch, load balancing, performance monitoring, OAM, 100ms buffering, header compression, IPSec encryption, and IP fragmentation.

The SmartNIC provides deterministic performance and its programmability enables scalability and future-readiness. Some of the applications that the ACE‑NIC40 enables and/or accelerates include OVS offload, SD-WAN and vCPE.

Ethernity Networks’ Router-on-NIC feature provides a high-performance switch/router data plane including Carrier Ethernet Switch, Layer 3 forwarding, protocol interworking, and traffic management, ideal for any application that requires the agility of a virtual router with the performance of a physical router appliance. Router-on-NIC differentiates the ACE-NIC40 from other SmartNICs.

- 40G non-blocking throughput

- OpenFlow-enabled

- Protocol interworking, including support for 3GPP gateway, VxLAN, NVGRE, PB, QinQ, IP and others

- 256K entries search filter

- Per-flow rules, including header manipulation, filtering, switching, time stamping and programmable header compression

- Router-on-NIC capability

- Load balancing at VM granularity

- Integrated packet generator and analyser to support wire speed OAM/CFM functions

- Programmable fragmentation and reassembly

- Per-frame nanosecond accuracy time stamping

- Wire speed NAPT

- Hierarchical queuing, scheduling and shaping

- L2/L3/L4 switch

- Optional IPSec Tunnel available per project

Related Products

Related Items

Contact Us

Related Solutions

Network Security on FPGA

Carrier Ethernet on FPGA

SD WAN Acceleration

NFVI Acceleration

vRouter VNF Acceleration